- 您现在的位置:买卖IC网 > Sheet目录3881 > PIC18F8585T-I/PT (Microchip Technology)IC PIC MCU FLASH 24KX16 80TQFP

2004 Microchip Technology Inc.

DS30491C-page 285

PIC18F6585/8585/6680/8680

23.2.2

DEDICATED CAN TRANSMIT

BUFFER REGISTERS

This section describes the dedicated CAN Transmit

Buffer registers and their associated control registers.

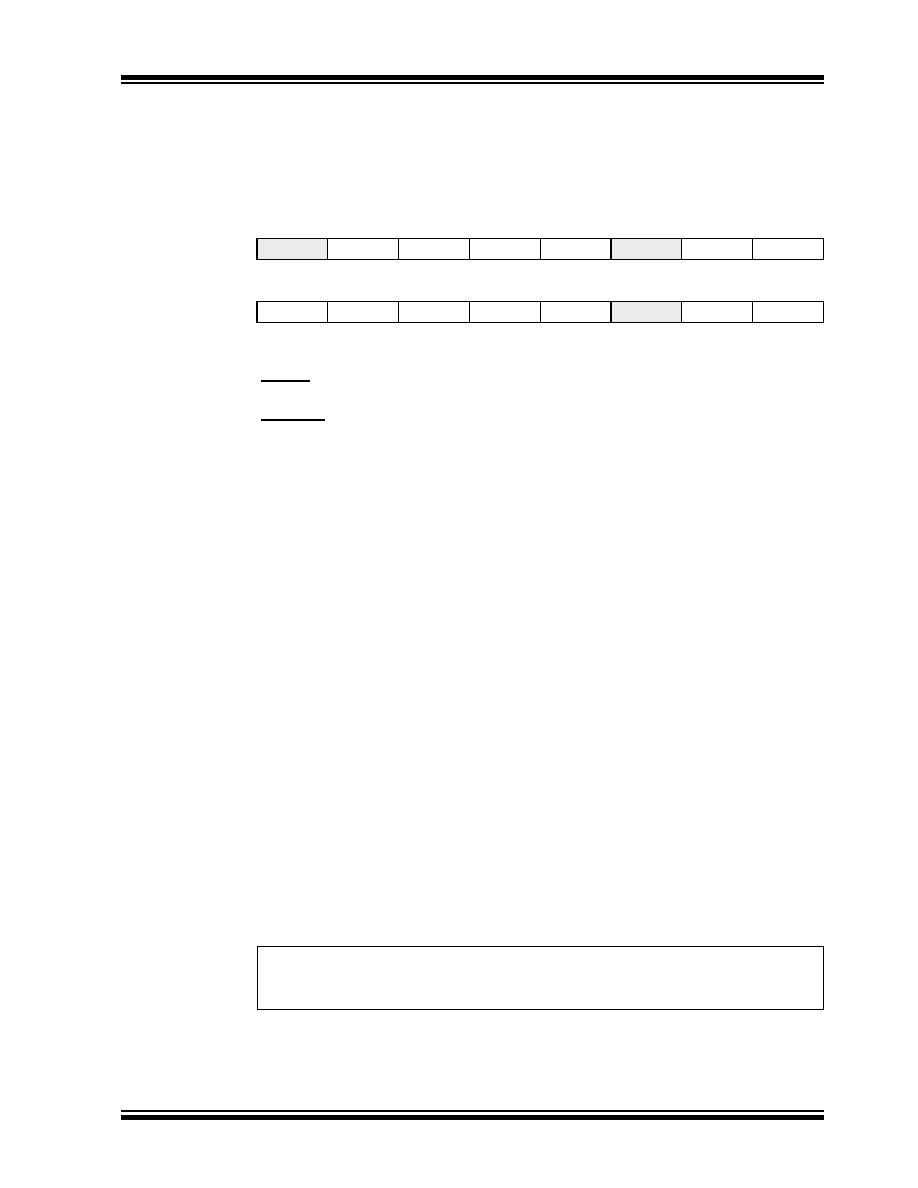

REGISTER 23-5:

TXBnCON: TRANSMIT BUFFER n CONTROL REGISTERS [0

≤ n ≤ 2]

Mode 0

U-0

R-0

R/W-0

U-0

R/W-0

—

TXABT

TXLARB

TXERR

TXREQ

—

TXPRI1

TXPRI0

Mode 1, 2

R/C-0

R-0

R/W-0

U-0

R/W-0

TXBIF

TXABT

TXLARB

TXERR

TXREQ

—

TXPRI1

TXPRI0

bit 7

bit 0

bit 7

Mode 0:

Unimplemented: Read as ‘0’

Mode 1, 2:

TXBIF: Transmit Buffer Interrupt Flag bit

1

= Transmit buffer has completed transmission of message and may be reloaded

0

= Transmit buffer has not completed transmission of a message

bit 6

TXABT: Transmission Aborted Status bit(1)

1

= Message was aborted

0

= Message was not aborted

bit 5

TXLARB: Transmission Lost Arbitration Status bit(1)

1

= Message lost arbitration while being sent

0

= Message did not lose arbitration while being sent

bit 4

TXERR: Transmission Error Detected Status bit(1)

1

= A bus error occurred while the message was being sent

0

= A bus error did not occur while the message was being sent

bit 3

TXREQ: Transmit Request Status bit(2)

1

= Requests sending a message. Clears the TXABT, TXLARB, and TXERR bits.

0

= Automatically cleared when the message is successfully sent

Note:

Clearing this bit in software while the bit is set, will request a message abort.

bit 2

Unimplemented: Read as ‘0’

bit 1-0

TXPRI1:TXPRI0: Transmit Priority bits(3)

11

= Priority Level 3 (highest priority)

10

= Priority Level 2

01

= Priority Level 1

00

= Priority Level 0 (lowest priority)

Note 1: This bit is automatically cleared when TXREQ is set.

2: While TXREQ is set, Transmit Buffer registers remain read-only.

3: These bits define the order in which transmit buffers will be transferred. They do not

alter the CAN message identifier.

Legend:

U = Unimplemented bit, read as ‘0’

- n = Value at POR

C = Clearable bit

R = Readable bit

W = Writable bit

x = Bit is unknown

‘1’ = Bit is set

‘0’ = Bit is cleared

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

XF2J-2424-11

CONN FPC 24POS 0.5MM SMT

PIC18LF6585T-I/PT

IC PIC MCU FLASH 24KX16 64TQFP

PIC18LF6680T-I/PT

IC PIC MCU FLASH 32KX16 64TQFP

XF2J-2224-11

CONN FPC 22POS 0.5MM SMT

PIC18F6525T-I/PT

IC PIC MCU FLASH 24KX16 64TQFP

PIC18F4439-E/ML

IC PIC MCU FLASH 6KX16 44QFN

XF2J-2024-11

CONN FPC 20POS 0.5MM SMT

PIC16LF747-I/ML

IC PIC MCU FLASH 4KX14 44QFN

相关代理商/技术参数

PIC18F85J10-I/PT

功能描述:8位微控制器 -MCU 32 KB FL 2 KB RAM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F85J10-I/PT

制造商:Microchip Technology Inc 功能描述:IC 8BIT MCU PIC18F 40MHZ TQFP-80 制造商:Microchip Technology Inc 功能描述:IC, 8BIT MCU, PIC18F, 40MHZ, TQFP-80

PIC18F85J10T-I/PT

功能描述:8位微控制器 -MCU 32 KB FL 2 KB RAM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F85J11-I/PT

功能描述:8位微控制器 -MCU 32KB Flash 2048BRAM 67I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F85J11T-I/PT

功能描述:8位微控制器 -MCU 32KB Flash 2048bytes-RAM 67I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F85J15-I/PT

功能描述:8位微控制器 -MCU 48 KB FL 4 KB RAM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F85J15T-I/PT

功能描述:8位微控制器 -MCU 48 KB FL 4 KB RAM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F85J50-I/PT

功能描述:8位微控制器 -MCU 32KB Flash 3936byte RAM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT